A3000, A500/R200, A5000, A3010, A3020, A4000, A4

Copyright (C) Acorn Computers Limited 1993

Published by Acorn Computers Technical Publications Department

Neither the whole nor any part of the information contained in, nor the product described in this manual may be adapted or reproduced in any material form except with the prior written approval of Acorn Computers Limited.

The products described in the manual are not intended for use as a critical component in life support devices or any system in which failure could be expected to result in personal injury.

The products described in this manual, and products for use with it are subject to continuous development and improvement. All information of a technical nature and particulars of the products and their use (including the information and particulars in this manual) are given by Acorn Computers Limited in good faith. However, Acorn Computers Limited cannot accept any liability for any loss or damage arising from the use of any information or particulars in this manual, or any incorrect use of the products. All maintenance and service on the products must be carried out by Acorn Computers' authorised dealers or Approved Service Centres. Acorn Computers Limited can accept no liability whatsoever for any loss or damage caused by service, maintenance or repair by unauthorised personnel.

IBM is a trademark of International Business Machines Corporation.

Within this publication, the term "BBC" is used as an abbreviation for "British Broadcasting Corporation".

Published by Acorn Computers Limited Part number xxxx Issue 1, March 1993

## Contents

| Introduction                                                                                  |                                                             | 1                     |

|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------|-----------------------|

| VIDC overview                                                                                 |                                                             | 1                     |

| Video Interface Descriptions:                                                                 |                                                             |                       |

| A3000                                                                                         | System Summary                                              | 1                     |

| A3000                                                                                         | Connectors and Links                                        | 1                     |

| A3000                                                                                         | Video Output Circuit                                        | 2                     |

| A540/R260                                                                                     | System Summary                                              | 2                     |

| A540/R260                                                                                     | Connectors and Links                                        | 2                     |

| A540/R260                                                                                     | Video Output Circuit                                        | 3                     |

| A5000                                                                                         | System Summary                                              | 3                     |

| A5000                                                                                         | Connectors and Links                                        | 3                     |

| A5000                                                                                         | Video Output Circuit                                        | 4                     |

| A5000                                                                                         | ROB Enhancements                                            | 4                     |

| A5000                                                                                         | Monitor Types                                               | 4                     |

| A5000                                                                                         | Monitor Sensing                                             | 4                     |

| A3010, A3020 and A4000                                                                        | System Summary                                              | 5                     |

| A3010, A3020 and A4000                                                                        | Connectors and Links                                        | 5                     |

| A3010, A3020 and A4000                                                                        | Video Output Circuit                                        | 5                     |

| A3010                                                                                         | Colour TV Encoder                                           | 5                     |

| A4                                                                                            | System Summary                                              | 5                     |

| A4                                                                                            | RGB Connector                                               | 5                     |

| A4                                                                                            | Video Output Circuit                                        | 6                     |

| A4                                                                                            | LC ASIC Description                                         | 6                     |

| A4                                                                                            | LC ASIC Functions                                           | 6                     |

| ROB Timing Parameters<br>Monitor Type 0<br>Monitor Type 1<br>Monitor Type 2<br>Monitor Type 3 | Key Diagram<br>Mode Timings<br>Mode Timings<br>Mode Timings | 7<br>7<br>8<br>9<br>9 |

| Monitor Type 4                                                                                | Mode Timings                                                | 9                     |

| Monitor Type 5                                                                                | Mode Timings                                                | 9                     |

March 1993

Page

### Introduction

This document outlines the Video systems implemented on the following current Acorn machines.

| • | A3000             | 9 w PGA              |

|---|-------------------|----------------------|

| • | A500/R200         | 9 w PGA              |

| • | A3010/A3020/A4000 | 15w VGA (enhanced)   |

| • | A5000             | 15w VGA (enhanced)   |

| • | A4 portable       | 15w VGA (enhanced)   |

|   |                   | built in LCD display |

It is assumed that the reader is familiar with the basic concepts of computer systems built around the ARM micro-processor unit (MPU) and its associated support devices, MEMC, VIDC and IOC. Some background information on VIDC implementation is detailed in VIDC overview.

In this document logic low active signals are indicated by a backslash / before the signal name,

Detailed specifications on the ARM chip set can be found in the Prentice Hall publication:

Acorn RISC Machine Family Data Book ISBN 0-13-781618-9.

### VIDC Overview.

The Video controller uses three buffers in RAM to generate three functions, a video display, a hardware cursor and stereo sound. The memory controller ( MEMC) coordinates the transfers from these buffers to VIDC by Direct Memory Access (DMA). The Video controller requests data from memory when required, and stores it in one of three internal "first-in, first-out" ( FIFO) buffers. Data is requested in blocks of four 32-bit wide words, allowing efficient use of page-mode DRAM without slowing down the system data bus for long periods.

The data from these buffers is serialised via digital to analogue converters (DACs). Video data is checked with a colour look-up palette, before being converted to analogue signals, red, green and blue (RGB) for video monitors. The use of DACs allows minimal external buffering for audio systems or video monitors.

Three forms of video synchronisation pulses are generated with programmable timing and polarity. The video clock may be selected from a variety of sources, and appears on external pins to allow the video to be genlocked to an external source.

The video controller is programmable offering a variety of display formats. The pixel rate can be selected from a range of sources and programmable pre-scaling applied. Video data be serialised to 8,4,2 or 1 bits per pixel. The horizontal timing parameters can be controlled to units of two pixels, and the vertical timing is controlled to units of one raster.

The 13 bit colour look-up palette to the DACs allows a choice from 4096 colours, or an external video source.

The hardware cursor is 32 pixels wide and may be any number of rasters high. It can be positioned anywhere on the screen. Three simultaneous colours(from a palette of 4096) are supported, and any pixel can be defined as transparent, which makes it possible to define cursors of varied shape.

The sound system on VIDC incorporates an exponential DAC and stereo image table for generation of high quality sound. Up to 8 channels are supported, each with a separate stereo position.

### Video Interface Descriptions.

#### A3000 System Summary

The A3000 uses a standard combination of ARM2 CPU and MEMC + data bus controlling VIDC.

### A3000 Connectors and Links

The A3000 has a 9 way D-type RGB video socket. This has a standard IBM PC PGA pin layout (SK14)

| 1                            | Red                                                                          |

|------------------------------|------------------------------------------------------------------------------|

| 2                            | Green                                                                        |

| 3                            | Blue                                                                         |

| 4                            | Horizontal or Composite Sync (Link 24)                                       |

| 5                            | V.Sync or Mode (Link 25)                                                     |

| 6,7,8,9                      | 0V                                                                           |

|                              | deo levels are 0.7V PK-Pk into 75 Ohm<br>bltage levels >= 2.0V (TTL) into 75 |

|                              | An asterisk * indicates default                                              |

| Link 24                      | Link pins 1,2 for H.Sync                                                     |

|                              | Link pins 2,3 for C.Sync *                                                   |

| Link 25 Link pins for V.Sync |                                                                              |

|                              | No link for Mode                                                             |

| (A3000                       | International)                                                               |

| (Link 25                     | 5 Link pins 1,2 for V.Sync )                                                 |

|                              | Link pins 2,3 for Mode *)                                                    |

| Link 26                      | Linked H.Sync inverted                                                       |

|                              | No link H.Sync standard *                                                    |

| Link 27                      | Linked V.Sync inverted                                                       |

|                              | No link V.Sync standard                                                      |

|                              |                                                                              |

Issue 1

March 1993 (C) ACORN LTD

R. McDONNELL

1

The A3000 has a Monochrome Video Output Phono socket (SK 13) providing a monochrome composite video signal of 1V Pk-Pk (0.7V video and 0.3V sync) into a 75 ohm load. Negative sync, positive video.

Link pins within the machine are provided to facilitate connection to a Genlock interface.

| Link 28 pin 1<br>pin 2 | Ckvidc<br>/Clksys            |                              |

|------------------------|------------------------------|------------------------------|

| Link 29 pin 1<br>pin 2 |                              |                              |

| -                      | /V.Sync or C.Sync<br>/H.Sync |                              |

| Link 31 pin 1<br>pin 2 | 1 2                          | (On issue 1)<br>(On issue 1) |

Genlock Signal Descriptions:

Ckvidc: VIDC master clock input. (TTL). VIDC resynchronises all it's inputs to this reference allowing the display frequency to be independent of processor and system tinting.

/Clksys: 24MHz sytem clock. CMOS, buffered signal supplying MEMC with a master clock reference used to derive all system timing functions. This is often used to supply Ckvidc, with a shorting link on Link 28.

Sink: External synchronisation pulse, TTL level input. A high on this signal resets the vertical timing counter and if an interlaced signal display is being used, the odd field is selected. The horizontal timing counter and all other registers are unaffected by this signal.

/V.Sync or C.Sync CMOS level output. Depending on bit seven of the Control Register, *this* pin will be either /V.Sync or C.Sync. V.Sync pulse width supplied by VIDC is programmable in units of a raster and if selected is active low. The C.Sync signal is the XNOR of /V.Sync and /H.Sync

/H.Sync This is a CMOS level output required by some monitors. It is also used by MEMC to discriminate between Cursor and Video requests. The pulse is active low, and the pulse width supplied by VIDC is programmable in units of 2 pixels.

/SUP: Supremacy CMOS level output signal. The signal can control a multiplexer between VIDC outputs and an external source for video mixing. If bit 12 of the Video or Cursor palette for any logical colour is set /SUP is driven low when that logical colour is displayed. So any logical colour can be defined as supreme or not, on a pixel by pixek basis.

### A3000 Video Output Circuit.

Each Video output signal from VIDC is a current sink with respect to the filtered video +5V supply. The signals (Red, Green and Blue) generate a voltage across a sense resistor and a PNP transistor.

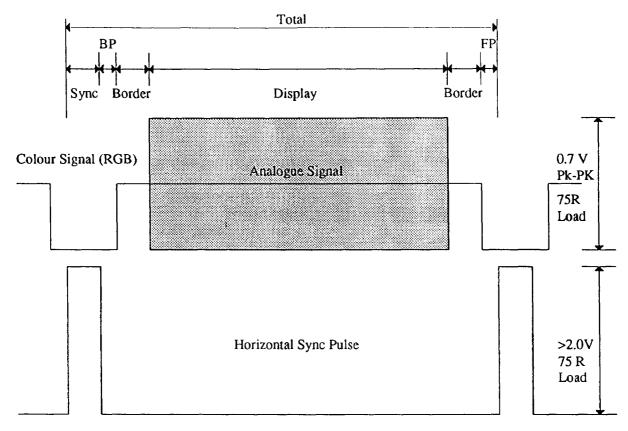

The voltage across the sense circuit is converted to an output current per colour, by a PNP transistor emitter follower. Another set of three PNP transistors are used in common mode to sum the three signals which are then added to /Composite Sync to provide the Composite Monochrome video out on SKT 13. The RGB monitor output components and Monochrome output components are protected from transients by a three diode circuit for each colour signal. A 220R load resistor limits the maximum unterminated voltage at each transistor collector; this ensures the transistor does not saturate and disturb the sense resistor signal. In normal use the RGB outputs generate an analogue 0.7V peak signal into an external 75R load to GND.

Separate or composite sync signals can be generated within VIDC under software control When selected, the Composite Sync signal appears on the V.Sync line. Sync signal outputs use a Cmos driver with a 68R resistor in series. The sync output can drive a monitor with TTL level inputs, typical of VGA and multifrequency monitors, or an analogue 75R terminated sync input.

### A540/R260 System Summary

A540/R260 systems use a combination of ARM 3 (on a daughter card) with MEMC, databus and Video clock MUX to control VIDC.

#### A540/R260 Connectors and Links

These machines have a 9 way D-type RGB video socket with a standard IBM PC PGA pin layout (SKT 2)

This is an identical pinout to that described for the A3000 (SKT 14) as are the RGB and Sync voltage levels. An additional link is provided to allow Sync on Green

SKT 12 High resolution mono video output. Provides a 0.7V mono video signal into 75 Ohm at a dot rate of 96 MHz. This requires a high resolution monitor to be connected.

SKT 13 High res mono Vertical/Composite Sync.

SKT 14 High res mono Horizontal Sync.

Link 1 Internal auxiliary video connector ( molex pins) providing access to the following signals:

- Red

Green or Sync on Green (Link 2)

Blue

Horizontal or Composite Sync (Link 6)

V.Sync or Mode (Link 3)

0 V

- Issue 1 March 1993 (C) ACORN LTD R. McDONNELL 2

|        | An asterisk * indicates default |   |

|--------|---------------------------------|---|

| Link 2 | Link pins 1,2 for Sync on green |   |

|        | Link pins 2,3 for normal Sync   | * |

- Link 3 Link pins 1,2 for V.Sync to ROB D-type pin 5 Link pins 2,3 for Mode to pin 5 \*

- Link 6 Link pins 1,2 for H.Sync to RGB D-type pin 4 Link pins 2,3 for CSync to pin 4 \*

A Video control latch (&3350048) is used by the operating system to control clock speed and video sync polarity appearing at SKT2, SK13/14 and Link 1. These data bits are latched and provide the following:

| DB0<br>DB0<br>DB0<br>DB0 | 0<br>0<br>1<br>1 | DB1<br>DB1<br>DB1<br>DB1 | 1<br>0 | 24 MH<br>25.175<br>36 MH<br>Reserv | MHz<br>z |

|--------------------------|------------------|--------------------------|--------|------------------------------------|----------|

|                          |                  |                          |        | V.Sync                             | H.Sync   |

| DB2                      | 0                | DB3                      | 0      | +ve                                | +ve      |

| DB2                      | 0                | DB3                      | 1      | +ve                                | -ve      |

| DB2                      | 1                | DB3                      | 0      | -ve +ve                            |          |

|                          |                  | DB3                      |        |                                    |          |

Link 15 Genlock expansion I/F. This is two 2 rows of 8 Molex pins, numbered as shown below. As a default, shorting links connect pins 1-2, and 3-4.

|            | Pins |    |                |

|------------|------|----|----------------|

| Intck      | 1    | 2  | Ckvidc         |

| Sink       | 3    | 4  | OV             |

| NC         | 5    | 6  | NC             |

| /Ved 0     | 7    | 8  | /Ved 1         |

| /Ved 2     | 9    | 10 | /Ved 3         |

| /Supremacy | 11   | 12 | /Hi            |

| /H.Sync    | 13   | 14 | /V.Sync or C.S |

| 0 V        | 15   | 16 | 0V             |

Genlock Signal Descriptions

(See other Genlock Signal descriptions for A3000)

Intck: The clock output from a programmable clock signal multiplexer, enabled by the video latch allowing the clock frequencies shown above.

/Ved 0-3: Video external data outputs (CMOS) levels. The inverse of the four data bits fed to the red DAC are output on these pins. With an external serialiser a very high resolution monochrome display may be obtained, and is the basis of the high res monochrome output on SK13 for these machines. /HI: Horizontal I/F timing marker (CMOS o/p). With interlaced displays this signal goes low halfway along the raster, staying low until the end of the raster. If non-interlaced displays are used then this signal may be used for a programmable timer on each raster

#### A540/R260 Video Output Circuit

#### Differences from A3000:

The sync signal polarity is programmable and there is the additional facility to put Sync on the Green output.

The Monochrome video output uses video external data Ved[0-3] which is serialised using a shift register running at 96 MHz providing a high resolution Monochrome output.

#### A5000 System Summary

The A5000 machine uses ARM 3 in combination with MEMC and databus, with IOEB supplying CLK to control VIDC.

#### A5000 Connectors and Links

The A5000 machine has a 15 way mini D-type RGB video socket. (SK1)

| 1       | Red                      |

|---------|--------------------------|

| 2       | Green                    |

| 3       | Blue                     |

| 4       | ID 2                     |

| 5,6,7,8 | 0 V                      |

| 9       | +5V (750 mA fuse)        |

| 10      | 0V                       |

| 11      | ID 0                     |

| 12      | ID 1 or SCART function   |

| 13      | Horizontal Sync          |

| 14      | V.Sync or Composite Sync |

| 15      | ID 3                     |

The A5000 has no other external Video connector. Internal link pins are provided within the machine to facilitate connection to a Genlock Interface.

Link 6 Genlock interface.

This is identical to the Genlock I/F pin layout of the A540 series shown above. (Link 15) The signal descriptions are the same.

### A5000 Video Output Circuit

Differences from A3000:

The RGB signals generate a voltage across a sense resistor and a common super-diode, formed by a PNP transistor, ie the current sense for each channel is handled by one transistor instead of three. This means they are no longer completely isolated from each other and each colour will have a very slight effect ( considered negligible) on the other colours.

There is no monochrome output, or sync on green.

#### A5000 RGB Enhancements:

The pin layout of SK2 is very similar to a standard VGA pinout, but with several enhancements, detailed below:

• Pin 9 (normally, used for keying) is used to supply +5v specifically for powering an external UHF modulator. The output is protected by a 750mA fuse.

• Pin 12 provides +12V (source impedance = 1k5). This output is used to provide a SCART function switching signal for use with SCART TVs.

• Pin 15 is an input ID 3 which may be used in the future to identify standard monitor types.

### A5000 Monitor Types

The monitor types listed below are supported. A scheme of automatically sensing the monitor type connected to the computer is implemented. This scheme ensures that the user sees a picture regardless of whatever monitor type is connected to the computer and that, where possible, the complete list of modes available for the particular monitor type is made available.

|    | Monitor Type            | Modes            |

|----|-------------------------|------------------|

| 0: | TV frequency/SCART      | 0-17,24,33-36    |

|    | TV/UHF modulator        |                  |

| 1: | Multi-frequency monitor | 0-21,24-31,33-46 |

| 3: | VGA monitor             | 0-15,25-28,41-46 |

| 4: | VGA/Super VGA mon       | 0-15,25-31,41-46 |

The automatic sense scheme uses the four ID bit inputs (ID0-3) present on the video interface connector to detect die type of monitor connected to the computer. The ID bits are read directly by software, where data bits D0-D3 correspond to ID0-ID3. Monitors designed for use with IBM machines and compatibles use a coding system where these bits define the monitor type. The bits are either connected to 0V or are left open circuit in the monitor or monitor cable. All ID bits are connected to 4K7 pullups on the A5000 PCB.

For example a mono VGA monitor connects ID1 to 0V leaving ID0 and ID2 to float high. This ID system has been adopted and extended as shown in the table:

| Monitor Type      | ID S<br>ID3 | ettings<br>ID2 | ID1 | ID0   |

|-------------------|-------------|----------------|-----|-------|

| Mono VGA          | *           | 1              | 0   | 1     |

| Colour VGA        | *           | 1              | 1   | 0     |

| Colour SVGA       | *           | 0              | 1   | 0     |

| Multi-frequency   |             |                |     |       |

| (using comp sync) | *           | H.Sync         | 1   | 1     |

| TV/UHF mod SCART  | *           | 1              | 1   | HSync |

|                   |             |                |     | •     |

\* undefined

Note 1: If none of the ID bits are connected to 0V then the software will default to the TV frequency monitor.

Note 2: The H.Sync to ID bit connections are Acorn defined and are made in the monitor cable.

### A5000Monitor Sensing

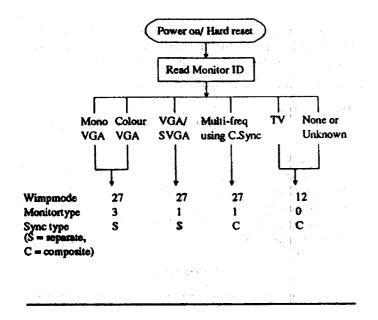

The \*Configure options: Monitortype, Sync and Wimpmode have an AUTO setting (eg. \*Configure Monitortype Auto) which determines the operation of the automatic monitor type sensing scheme.

At power-on or following a hard reset, with all three options set to AUTO, the software senses the monitor type and sets the Wimpmode, Sync type and Monitor type (which defines the list of available modes) for the particular monitor connected. These are temporary values which are not written back to the CMOS RAM. Subsequent \*Configure Monitortype, Sync or Wimpmodes selected by the user overwrite the relevant AUTO setting in CMOS RAM so the machine is initialised in the mode desired. A new power-on/reset sequence is the same as described above, except that software now uses the options selected by the user instead of the AUTO setting. See the figure Monitor Sensing on the following page.

Most Multi-frequency monitors have their ID bits set as if they were a VGA or Super VGA monitor, and monitor type 1 modes will be available when using the monitor sensing scheme, as many Multi-frequency monitors are capable of displaying some or all of the monitor type 1 modes. To use genuine SVGA monitors re-configure the CMOS RAM setting to monitor type 4.

March 1993

### A3010/A3020/A4000 System Summary

These systems use the ARM250 combination chip. This contains an ARM 2AS processor, MEMC. IOC and VIDC all within a single chip, and so the overall system architecture is fundamentally the same.

### A3010/A3020/A4000 Connectors & links

These systems have a 15 way mini D-type RGB video socket (SK1) with the same pin layout and specification as that described for the A5000, including the enhanced monitor sense protocol.

A Genlock interface is provided, signal pins as follows.

| Link 6  | PI | NS |                |

|---------|----|----|----------------|

| /H.Sync | 1  | 2  | /V. or /C.Sync |

| sink    | 3  | 4  | 0V             |

| Vidclk  | 5  | 6  | Clkvid         |

| 0V      | 7  | 8  | /Sup           |

The signal descriptions are identical to those described for the A3000.

### A3010/A3020/A4000 Video Output Cct

### Differences from A3000:

A3010, A3020 and A4000 are identical to A5000.

A3010 also has a pair of emitter followers for each colour. One set is for RGB monitor signals, and the other is for the TV colour encoder circuit detailed below.

Separate or composite sync signals can be generated within the ARM 250; selection is software controlled. When selected, the Composite Sync signal appears on the V.Sync line. Sync signals are CMOS buffered.

### A3010 TV Colour Encoder

The RGB current sources driving the colour encoder each generate a a nominal 0.7V peak signal across a terminating 75R resistor. The RGB signals are capacitively coupled to the encoder Ic inputs. A Sony CXA1145 encodes the RGB video and TTL. composite sync signal into a colour video signal (ie; Video + composite sync + chroma (colour) signal).

The chroma signal can be set to PAL or NTSC formats. For PAL 1 (UK), a 4.4336 MHz crystal is used in the CXA1145 oscillator circuit. A trimmer capacitor allows the fine tuning of the carrier frequency. In practice the frequency is not critical for colour generation in a TV but the chroma frequency does beat/interfere with high frequency components in the luma signal. Careful trimming of the oscillator can reduce the subjective effects of the beat frequency.

The chrona signal is band-pass filtered before it is mixed with the delayed luma signal. The luma delay is chosen to match the chroma signal delay through the bandpass filter. the complete encoded signal is terminated with a two-resistor attenuator, which matches the signal level to the UHF modulator. A separate bias chain ensures the correct DC level is present at the rnodulator input. The modulator is a standard video plus sound unit which generates a low power UHF signal -on channel 35 (UK model).

### A4 System Summary

The system uses ARM3 in conjunction with MEMC and databus to control VIDC. For the LCD display there is a controller ASIC (LC ASIC), which also controls VIDC clock signal.

### A4 RGB Connector

This machine is fitted with a 15 way mini-din Video RGB connector (SK6). The pin out is identical to A5000 and Monitor types are sensed using ID bits in the same way.

A4 also supports monitor type 5 which is the LCD screen option. If nothing is connected to SK6 then the machine assumes the LCD is required. A summary. of Monitor types supported by A4 machines are shown below.

March 1993

| Ν    | Monitor Type                           | Modes             |

|------|----------------------------------------|-------------------|

| 0:   | TV frequency/SCART<br>TV/UHF modulator | 0-17,24,33-36     |

| 1:   | Multi-frequency monitor                | 0-21,24-31,33-46  |

| 3:   | VGA monitor                            | 0-15,25-28,41-46  |

| 4:   | VGA/Super VGA mon                      | 0-15,25-31,41-46  |

| 5:   | LCD screen                             | 0-17,24-28        |

| AUTO | Auto-configure                         | Monitor dependent |

There is no Genlock I/F, or monochrome output. There are no links for video functions.

### A4 Video Output Circuit

Differences from A3000:

The RGB output circuit is identical to that described for the A5000. The only slight mechanical difference is that the RGB signals from VIDC go to a video hybrid board, which contains the common super diode current sense circuitry, protection diodes and transistor drivers, before returning to the main PCB for connection to SK6.

### A4 LC ASIC Description

The LC asic provides a programmable interface to monochrome flat panel LCD displays offering 16 levels of grey scale. A large range of display formats are catered for including 320X200 and 640X200 single panel displays as well as 640X400 and 640X480 dual panel displays.

The device accepts pixel data, and horizontal and vertical sync signals from VIDC. It re-times the image and converts it to grey scales for display on the LCD panel.

When used to control a dual panel display, one or two external DRAMS are needed to act as a half frame buffer. The LC ASIC supports a wide variety of DRAMs, though in most applications, two 64Kx4 devices are sufficient.

### A4 LC ASIC Functions

The following functional blocks are contained within the LC ASIC.

CLOCK: Clock and reset inputs used with LC's crystal oscillator provide clock selection and control for LC and VIDC.

VIDC I/F: The VIDC interface block synchronises incoming video data and sync signal, and inverts incoming data before performing a logical to physical colour translation. It does this by looking up the logical colour on the 16 entry on-chip palette.

REGISTERS: This functional block contains all the software programmable bits in the device and outputs them to other parts of the chip via the Control logic block.

CONTROL: This generates all the internal control logic signals.

GREY SCALE: The grey scale block takes input from the VIDC interface post-palette data and control block to provide Grey scale video data to the DRAM block.

DRAM: This block takes data input from the Grey scale block, together with Control and Clock signals, in order to store data temporarily in the external DRAM devices, generating all necessary timing and control signals for them. The DRAM block also outputs the data to the LCD panel; with the correct timing.

### RGB Key Diagram

| Monitor Typ                    | pe 0               | Back                |                      |                         | Horiz                | ontal P<br>Front    | arame                  |                   | frag                 | Display                       | Pixel             |

|--------------------------------|--------------------|---------------------|----------------------|-------------------------|----------------------|---------------------|------------------------|-------------------|----------------------|-------------------------------|-------------------|

| Mode<br>0,3,4,8,11<br>12,14,15 | Sync<br>76<br>4.75 | Porch<br>89<br>5.56 | Border<br>96<br>6.00 | Display<br>640<br>40.00 | Border<br>96<br>6.00 | Porch<br>27<br>1.69 | Total<br>1024<br>64.00 |                   | .freq<br>Hz<br>5.625 | Display<br>Center uS<br>36.31 | Rate KHz<br>16000 |

| 1,2,5,6,7<br>9,10,13           | 38<br>4.75         | 45<br>5.62          | 48<br>6.00           | 320<br>40.00            | 48<br>6.00           | 13<br>1.62          | 512<br>64.00           | pixels 15<br>uSec | 5.625                | 36.37                         | 24000             |

| 16,17,24                       | 114<br>4.75        | 133<br>5.54         | 96<br>4.00           | 1056<br>44.00           | 96<br>4.00           | 41<br>1.71          | 1536<br>64.00          | pixels 15<br>uSec | 5.625                | 36.29                         | 16000             |

| 33,35,35,36<br>(overscan)      | 76<br>4.75         | 121<br>7.56         | 0<br>0               | 768<br>48.00            | 0<br>0               | 59<br>3.69          | 1024<br>64.00          | pixels 15<br>uSec | 5.625                | 36.31                         | 16000             |

| TV nominal                     | 76<br>4.75         | 90<br>5.65          | 0<br>0               | 832<br>52.00            | 0<br>0               | 26<br>1.60          | 1024<br>64.00          | pixels<br>uSec    |                      | 36.40                         | 16000             |

| Monitor Typ                    | pe 0               |                     | Note; l              | Raster va               | alues in t           | orackets            | apply fo               | r Risc OS         | 2 inste              | ad of Risc OS                 | 3.                |

| 0124580                        |                    |                     |                      |                         | Vertic               | al Para             | meter                  |                   | H.freq<br>Hz         | Vertical<br>Center            |                   |

| 0,1,2,4,5,8,9<br>10,12,13,15   | 3                  | 19(20)              | 16                   | 256                     | 16(15)               | 2                   | 312                    |                   | 50.08                | 166                           |                   |

| 3,6,7,11,14,17                 | 3                  | 19(20)              | 19                   | 250                     | 19(18)               | 2                   | 312                    | rasters .         | 50.08                | 166                           |                   |

| 33,34,35,36                    | 3                  | 19                  | 0                    | 288                     | 0                    | 2                   | 312                    | rasters .         | 50.08                | 166                           |                   |

| Issue 1 | March 1993 | (C) ACORN LTD | R. McDONNELL | 7_ |

|---------|------------|---------------|--------------|----|

|         |            |               |              |    |

| <b>Monitor Ty</b>              | pe 1              | Horizontal Parameters       |                     |                         |                     |                              |                        |                                        |                               |                            |  |

|--------------------------------|-------------------|-----------------------------|---------------------|-------------------------|---------------------|------------------------------|------------------------|----------------------------------------|-------------------------------|----------------------------|--|

| Mode<br>0,3,4,8,11<br>12,14,15 | Sync<br>72<br>4.5 | Back<br>Porch<br>63<br>3.94 | Border<br>88<br>5.5 | Display<br>640<br>40.00 | Border<br>88<br>5.5 | Front<br>Porch<br>73<br>4.56 | Total<br>1024<br>64.00 | H.freq<br>KHz<br>pixels 15.625<br>uSec | Display<br>Center uS<br>33.94 | Pixel<br>Rate KHz<br>16000 |  |

| 1,2,5,6,7<br>9,10,13           | 36<br>4.5         | 31<br>3.87                  | 44<br>5.5           | 320<br>40.00            | 44<br>5.5           | 37<br>4.62                   | 512<br>64.00           | pixels 15.625<br>uSec                  | 33.87                         | 8000                       |  |

| 16,17,24                       | 108<br>4.5        | 73<br>3.04                  | 106<br>4.42         | 1056<br>44.00           | 106<br>4.42         | 87<br>3.62                   | 1536<br>64.00          | pixels 15.625<br>uSec                  | 33.96                         | 24000                      |  |

| 33,35,35,36<br>(overscan)      | 76<br>4.75        | 83<br>5.19                  | 0<br>0              | 768<br>48.00            | 0<br>0              | 97<br>6.06                   | 1024<br>64.00          | pixels 15.625<br>uSec                  | 36.94                         | 16000                      |  |

| 18,19,20,21                    | 56<br>2.33        | 113<br>4.71                 | 0<br>0              | 640<br>26.67            | 0<br>0              | 87<br>3.62                   | 896<br>37.33           | pixels 26.786<br>uSec                  | 5 20.37                       | 24000                      |  |

| 25,26,27,28<br>(VGA)           | 96<br>3.81        | 47<br>1.87                  | 0<br>0              | 640<br>25               | 0<br>42 0           | 17<br>0.68                   | 800<br>31.78           | pixels 31.469<br>uSec                  | 18.39                         | 25175                      |  |

| 29,30,31<br>(SVGA)             | 100<br>2.78       | 101<br>2.81                 | 0<br>0              | 800<br>22.22            | 0<br>0              | 23<br>0.64                   | 1024<br>28.44          | pixels 35.156<br>uSec                  | 16.69                         | 36000                      |  |

| 37,38,39,40<br>(DTP-ega)       | 118<br>4.92       | 59<br>2.46                  | 0<br>0              | 896<br>37.33            | 0<br>0              | 27<br>1.12                   | 1100<br>45.83          | pixels 21.818<br>uSec                  | 26.04                         | 24000                      |  |

| 41,42,43<br>(EGA-pcemu)        | 76<br>4.53        | 37<br>2.2                   | 0<br>0              | 640<br>38.13            | 0<br>0              | 15<br>0.89                   | 768<br>45.76           | pixels 21.853<br>uSec                  | 25.8                          | 16783                      |  |

| 44,45,46<br>(CGA-pcemu)        | 72<br>4.5         | 163<br>10.19                | 0<br>0              | 640<br>40.0             | 0<br>0              | 145<br>9.06                  | 1020<br>63.75          | pixels 15.686<br>uSec                  | 5 34.69                       | 16000                      |  |

### **Monitor Type 1**

|                                       |   |    |    | H.freq | Vertical |    |             |             |               |

|---------------------------------------|---|----|----|--------|----------|----|-------------|-------------|---------------|

| 0,1,2,4,5,8,9<br>10,12,13,15<br>16,24 | 3 | 16 | 17 | 256    | 17       | 3  | 312 rasters | Hz<br>50.08 | Center<br>164 |

| 3,6,7,11,14,17                        | 3 | 16 | 20 | 250    | 20       | 2  | 312 rasters | 50.08       | 164           |

| 33,34,35,36                           | 3 | 19 | 0  | 288    | 0        | 2  | 312 rasters | 50.08       | 164           |

| 18,19,20,21                           | 3 | 18 | 0  | 512    | 0        | 1  | 534 rasters | 50.16       | 277           |

| 25,26,27,28                           | 2 | 32 | 0  | 480    | 0        | 11 | 525 rasters | 59.94       | 274           |

| 29,30,31                              | 2 | 22 | 0  | 600    | 0        | 1  | 625 rasters | 56.25       | 324           |

| 37,38,39,40                           | 3 | 9  | 0  | 352    | 0        | 0  | 364 rasters | 59.94       | 188           |

| 41,42,43                              | 3 | 9  | 0  | 352    | 0        | 0  | 364 rasters | 60.04       | 188           |

| 44,45,46                              | 3 | 34 | 0  | 200    | 0        | 25 | 262 rasters | 59.87       | 137           |

| Monitor Type 2 Horizontal Parameters |                    |                             |                      |                        |                       |                               |                       |                |                         |                                     |                            |

|--------------------------------------|--------------------|-----------------------------|----------------------|------------------------|-----------------------|-------------------------------|-----------------------|----------------|-------------------------|-------------------------------------|----------------------------|

| Mode<br>23<br>Hi res Mono            | Sync<br>52<br>2.17 | Back<br>Porch<br>47<br>1.95 | Border<br>2<br>0.08  | Display<br>288<br>12.0 | Border<br>2<br>0.08   | Front<br>Porch<br>1<br>0.04   | Total<br>392<br>16.33 | •              | H.freq<br>KHz<br>15.625 |                                     | Pixel<br>Rate KHz<br>24000 |

| Monitor Ty                           | vpe 2              |                             |                      |                        | Verti                 | cal Par                       | ramet                 | ers            |                         |                                     |                            |

| 23                                   | 3                  | 43                          | 4                    | 896                    | 4                     | 0                             | 950                   | rasters        |                         |                                     |                            |

| Monitor Ty                           | ype 3              |                             |                      |                        | Horiz                 | ontal ]                       | Paran                 | neters         |                         |                                     |                            |

| Mode.<br>0,3,4,8,11<br>12,14,15 3.81 | Sync<br>96<br>1.87 | Back<br>Porch<br>47<br>0    | Border<br>0<br>25.42 | 640                    | y Border<br>0<br>0.68 | Front<br>Porch<br>17<br>31.78 | Total<br>800<br>uSec  | pixels         | H.freq<br>KHz<br>31.469 | Display<br>Center uS<br>18.39 2517: | Pixel<br>Rate KHz<br>5     |

| 1,2,5,6,7,9<br>10,13                 | 48<br>3.81         | 23<br>1.83                  | 0<br>0               | 320<br>25.42 0         | 0<br>0 0.71 31.       | 9<br>78 uSec                  | 400                   | pixels         | 31.469                  | 18.35                               | 12587                      |

| VGA nominal<br>12,14,15              | 96<br>3.81         | 40<br>1.59                  | 0<br>0               | 656<br>26.06           | 0<br>0                | 8<br>0.32                     | 800<br>31.78          | pixels<br>uSec | 31.46618                | 3.43                                | 25175                      |

| Monitor Ty                           | ype 3              |                             |                      |                        |                       |                               |                       |                |                         |                                     |                            |

|                                      |                    |                             |                      |                        | Verti                 | cal Pa                        | ramet                 | ers            | H.freq<br>Hz            | Vertical<br>Center                  |                            |

| 10,12,13,15<br>16,24                 | 2                  | 106                         | 0                    | 256                    | 0                     | 85                            | 449                   | rasters        |                         | 236                                 |                            |

| 3,6,7,11,14,17                       | 2                  | 109                         | 0                    | 250                    | 0                     | 88                            | 449                   | rasters        | 70.09                   | 236                                 |                            |

### Monitor type 4 (VGA/SVGA)

2

53

0

Monitor type 4 parameters are the same as all monitor type three modes, plus Monitor type 1 parameters for modes 25, 26,27,28 (VGA) and 29,30,31 (SVGA)

0

32

449

**Horizontal Parameters**

rasters 70.08 236

362

### Monitor Type 5 (LCD)

VGA 350, nom

| Mode<br>0,3,4,8,11<br>12,14,15<br>25,26,27,28<br>41,42,43,44<br>45,46 |           | Back<br>Porch<br>175<br>7.29 | Border<br>0<br>0 | Display<br>640<br>26.67 | Border<br>0<br>0 | Front<br>Porch<br>269<br>11.21 | Total<br>1192<br>49.67 | pixels<br>uSec | H.freq<br>KHz<br>20.134 | Display<br>Center uS<br>25.12 | Pixel<br>Rate KHz<br>24000 |

|-----------------------------------------------------------------------|-----------|------------------------------|------------------|-------------------------|------------------|--------------------------------|------------------------|----------------|-------------------------|-------------------------------|----------------------------|

| 1,2,5,6,7,9<br>10,13                                                  | 54<br>4.5 | 87<br>7.25                   | 0<br>0           | 320<br>26.67            | 0<br>0           | 135<br>11.25                   | 596<br>49.67           | pixels<br>uSec | 20.134                  | 25.08                         | 12000                      |

| Issue 1 | March 1993     | (C) ACORN LTD  | R. McDONNELL | 9 |

|---------|----------------|----------------|--------------|---|

| 100000  | 1.141.011 1//0 | (0)11001111212 |              |   |

| Monitor Ty  | pe 5 ( | LCD)          |        | V       |        |                 |     |         |              |                    |

|-------------|--------|---------------|--------|---------|--------|-----------------|-----|---------|--------------|--------------------|

| Mode        | Sync   | Back<br>Porch | Border | Display | Border | Fron<br>r Porcl |     |         | H.freq<br>Hz | Vertical<br>Center |

| 10,12,13,15 | 1      | 0             | 112    | 256     | 116    | 0               | 485 | rasters | 41.51        | 241                |

| 3,6,7,11,14 | 1      | 0             | 115    | 250     | 119    | 0               | 485 | rasters | 41.51        | 241                |

| 25,26,27,28 | 1      | 0             | 0      | 480     | 4      | 0               | 485 | rasters | 41.51        | 241                |

| 41,42,43    | 1      | 0             | 64     | 352     | 68     | 0               | 485 | rasters | 41.51        | 241                |

| 44,45,46    | 1      | 0             | 140    | 200     | 144    | 0               | 485 | rasters | 41.51        | 241                |